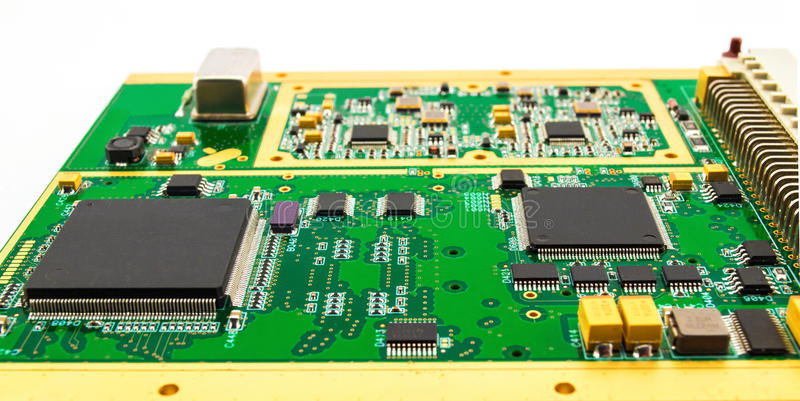

何為pcb設(shè)計(jì),?這是一種通過電路原理圖作為媒介實(shí)現(xiàn)電路設(shè)計(jì)者所需求多項(xiàng)功能的產(chǎn)品設(shè)計(jì)。

pcb設(shè)計(jì)不是易事,,需要考慮到方方面面,,既要綜合考慮外部連接的各種布局,還要評估內(nèi)部電子元件的優(yōu)化布局,。其中的元素包括有弱電保護(hù)問題還有熱耗散因素等,。優(yōu)秀的pcb設(shè)計(jì)可以將生產(chǎn)成本技術(shù)降低,言簡意賅的pcb設(shè)計(jì)更是滿足手工操作需求,,而復(fù)雜的pcb設(shè)計(jì)無疑要借助CAD制圖來實(shí)現(xiàn),。

那么,pcb設(shè)計(jì)途中會經(jīng)常遇到各種各樣的難題,,下面就針對一些難題進(jìn)行答疑:

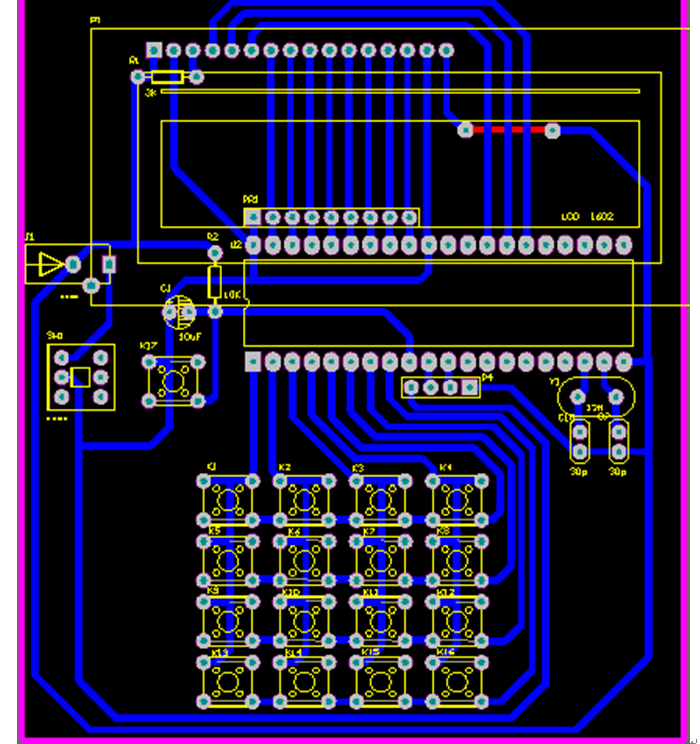

一是圖形層的濫用,。

在一些圖形層上進(jìn)行濫用,毫無疑問是一種耗材的浪費(fèi),。舉例說明下,,本來是五層板設(shè)計(jì),但卻被設(shè)計(jì)成了六層,,連接線的增多是不是對材料造成了耗費(fèi),。pcb設(shè)計(jì)絲毫不可以馬虎,,更加不能圖方便、圖省事,;可如果因?yàn)檫B接線的遺漏,,必然會造成斷路;如果是因?yàn)檫B接線標(biāo)注的問題導(dǎo)致短路時,,問題將更加嚴(yán)重,,所以在pcb設(shè)計(jì)的過程中必須要做到頭腦思緒清楚,以保證圖形層的完整,。

二是大面積的網(wǎng)絡(luò),,間距預(yù)留過分小。

要知道pcb設(shè)計(jì)是需要依托學(xué)術(shù)技術(shù)的,,一旦組成大面積網(wǎng)格線同線間的邊緣過分小時,,這里的小是指小于0.3毫米,必然導(dǎo)致在后期印制制造的過程中,,圖轉(zhuǎn)工序在顯示完影后事產(chǎn)生過多的碎膜附于板子上面,,這樣的現(xiàn)象會導(dǎo)致什么問題呢?即是造成斷線,。

三是表面貼裝器件焊盤過分短,。

在通斷測試的途中,在表面貼裝器件的設(shè)計(jì)過程中,,兩腳之間間距過分小,而且器件的排布過分密時,,一旦測試針安裝位置有交錯時,,雖然不會影響整體的器件安裝,卻也會導(dǎo)致測試針無法錯開位置,。

四是pcb設(shè)計(jì)途中塊填充過多,,或采用極線的線填充。

倘若pcb設(shè)計(jì)設(shè)計(jì)途中采用這種方法,,容易造成光繪數(shù)據(jù)的丟失現(xiàn)象,,也將導(dǎo)致光數(shù)據(jù)的不全面性,同樣還會導(dǎo)致數(shù)據(jù)處理的難度,,增加后面操作的繁瑣性和冗余性,。

五是pcb設(shè)計(jì)用填充畫焊盤。

怎么說呢,?pcb設(shè)計(jì)的目的是為了后期的生產(chǎn)加工,,雖然填充塊畫焊盤在設(shè)計(jì)的途中可以通過DRC的檢查,但是被投入到生產(chǎn)中卻是不行的,,因?yàn)檫@樣的焊般不可以直接生成阻焊數(shù)據(jù),,必然也就會導(dǎo)致器件焊裝的困難重重,。

六是pcb設(shè)計(jì)途中字符放置的不合理性。

千萬不要覺得這是個可以忽視的問題,,殊不知一葉瞥目帶來的危害性,。pcb設(shè)計(jì)途中,一旦字符設(shè)計(jì)的太小時,,就會導(dǎo)致絲網(wǎng)印刷的困難,,但是,如果字符被放置的過分大時,,就會導(dǎo)致它們間的相互重疊性,,就更加無法區(qū)分。

pcb設(shè)計(jì)途中遇到的難題答疑,?其時可能出現(xiàn)的問題有很多,,而上述的五點(diǎn)只是小編整理的一小部分,如果還有更多的疑惑就請繼續(xù)關(guān)注我們,,我們會定期為你提供pcb設(shè)計(jì)的相關(guān)知識點(diǎn),。